TSMC : des puces "wafer on wafer" en 5nm pour 2021

Par June Cantillon - Publié le

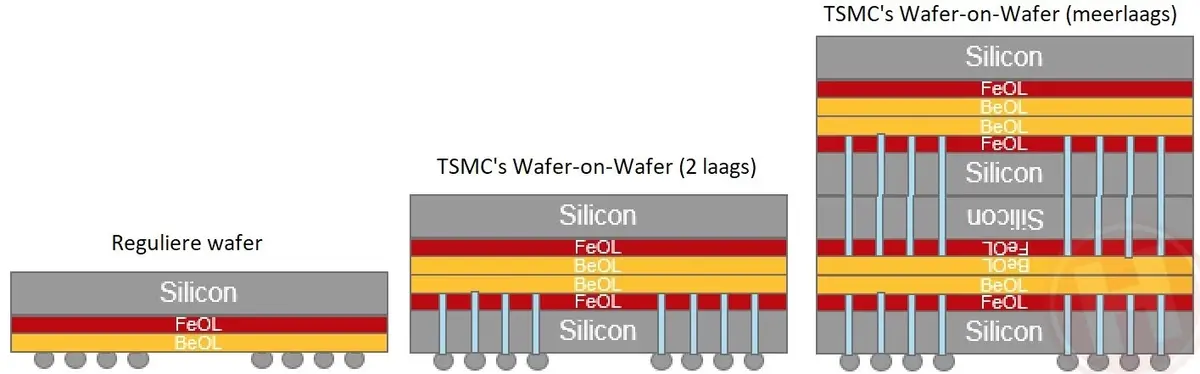

L'information est on ne peut plus officielle puisqu'elle provient de Wei Zhejia co-dirigeant de TSMC. Il annonce que les premières puces gravées en 5nm avec le procédé

wafer on wafer-ou WoW, un acronyme qui parlera aux fans de Blizzard- sortiront des usines du groupe en 2021. Cette technologie permet de créer des puces repliées sur elles-mêmes et profitant donc d'une double épaisseur.

Les deux

tranchesde la puce seront alimentées à l'aide de TSV -pour Through Silicon Vias- et permettront d'empiler des CPU, ou des GPU, augmentant nettement la puissance par rapport au volume occupé. TSMC s'est inspiré des technologies appliquées à la NAND 3D pour imaginer ces puces de nouvelle génération.

Le WoW de TSMC a été développé en partenariat avec Cadence Design Systems et combine les procédés InFO -pour Integrated Fan-Out- et CoWoS (pour Chip-on-Wafer-on-Substrate). Apple pourrait alors en profiter sur des puces AX maisons, fabriquées par TSMC selon ce procédé, permettant d'augmenter nettement le nombre de transistors disponibles pour une surface équivalente aux SoC précédents.

Source