De la NAND 3D 128 couches chez WD et Toshiba

Par June Cantillon - Publié le

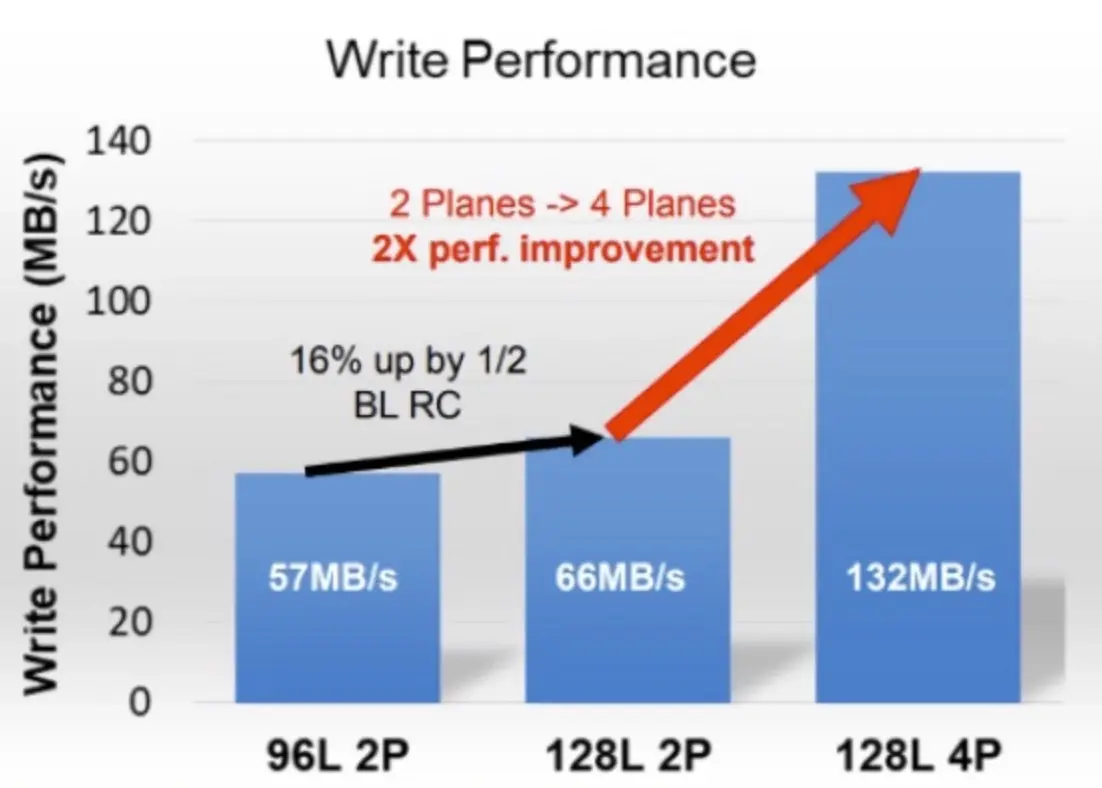

Les cellules seront de type TLC (3 bits par cellule), le QLC (4 bits par cellule) aurait été mis de côté en raison des taux élevés de puces défectueuses par wafer. Côté capacité, la NAND 3D 128 couches pourra culminer à 512 Go par puce, avec des débits en nette hausse, atteignant 132 Mo/s, et un temps d'accès réduit .

La technologie CuA employée -pour Circuitry under Array, plaçant le circuit logique à la base de l'empilement de couches- permettra également de réduire l'encombrement de 15%., et ainsi d'utiliser 4 plans au lieu de deux. Les premières machines équipées d'une telle mémoire ne devraient cependant pas être commercialisées avant l'année prochaine.

Source