Intel annonce le passage à 10nm pour fin 2017, et des performances en hausse de 25%

Par Didier Pulicani - Publié le

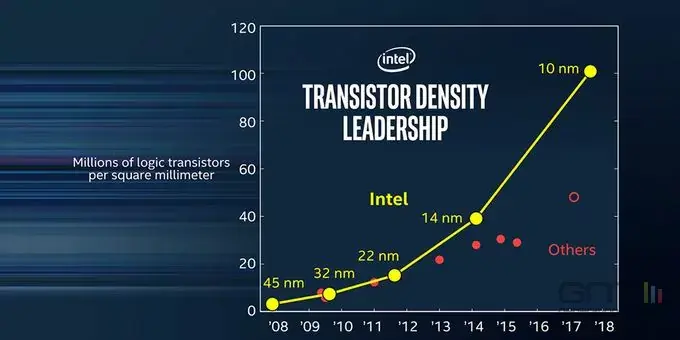

Alors que TSMC produit déjà des SoC à cette finesse de gravure (avec le Snapdragon 835 destiné à Samsung), la firme de Santa Clara estime pourtant rester leader sur le processus, qui lui permet de graver bien plus de transistors que ses concurrents à surface égale. La loi de Moore serait donc toujours d'actualité, avec une densité multipliée par 2,7 cette année. Intel insiste d'ailleurs sur le fait que la finesse de gravure n'est qu'un indicateur parmi d'autres, et que les chiffres annoncés par ses concurrents (TSMC en tête) ne sont pas forcément comparables.

Les premières puces Cannonlake devraient donc débarquer à la fin de l'année, et Intel annonce déjà un gain de performances de 25%, tout en réduisant la consommation de 45%. En parallèle, sortira également une dernière version des puces gravées en 14nm (Kaby Lake+ ?) qui ne devrait pas réellement bousculer la donne. L'architecture suivante (

toc, pour fin 2018 ?) pourrait encore gagner 15% en vitesse d'exécution et 30% sur la consommation, tout en restant évidemment sur du 10nm. Enfin, histoire de rassurer tout le monde, Stacy Smith a déclaré que les gravures à 5/7nm étaient déjà dans le viseur de la société.

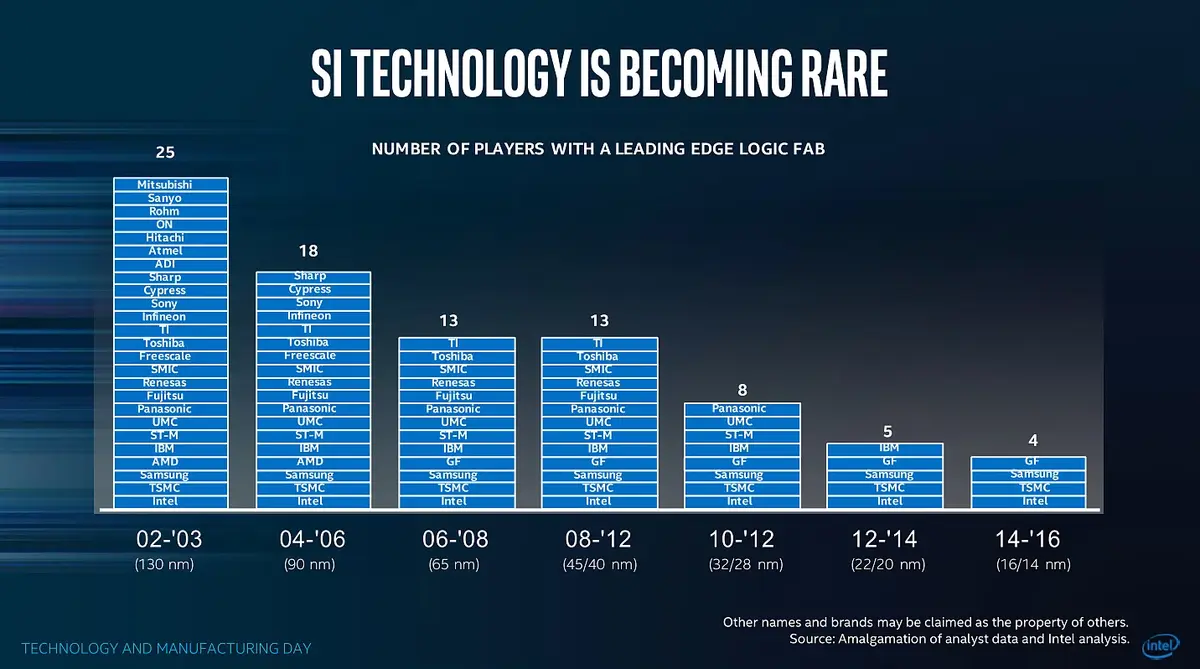

On en oublierait presque que les puces Intel font du quasi-surplace depuis 5/6 ans ! Ces annonces interviennent d'ailleurs dans un contexte bien particulier, où AMD reprend du poil de la bête, et se montre désormais très concurrentiel. Cela méritait bien une petite opération de communication... Intel ne cache d'ailleurs pas son échec sur les appareils mobiles où les puces ARM ont largement remporté la mise. A ce propos, la firme évoque un véritable constriction du marché des fondeurs, qui s'est réduit à seulement 4 acteurs, dont 2 sont ultra-financés par de grandes multinationales (dont Apple et Samsung). Tout cela pour dire qu'à l'arrivée, Intel

tient bonmalgré les enjeux de plus en plus complexes et coûteux sur le segment des semi-conducteurs.

Via